Intel has released details of its next-generation Xeon Phi Many Integrated Cores (MIC) chips, codenamed Knights Landing, including the promise of a standalone CPU based on a 14nm process node.

Designed to combat the growing trend for supercomputing and other high-performance customers to turn to graphics processing units-based accelerator boards like Nvidia's Tesla family for highly-parallel workloads, Xeon Phi is the first commercial product from Intel's Many Integrated Cores (MIC) project. Based on an x86 architecture roughly equivalent to the original Pentium, the first Xeon Phi is an add-in PCI Express card offering more than 50 processing cores and a stack of high-speed memory for highly parallel tasks.

According to details released by Intel at the Supercomputing Conference late yesterday, however, it won't always be this way. The next-generation version will also be available as a standalone CPU, constructed on a 14nm process node. Unlike the original Xeon Phi, the next-generation model will be able to operate entirely independently - executing both serial operating system tasks and parallel code on the same chip - with no need for a traditional CPU at all.

That's something that is likely to make the HPC market sit up and take notice. Traditional highly-parallel co-processing boards, whether GPU or CPU based in architecture, rely on having traditional processors to handle running the operating system and keeping the accelerators fed with data. This leads to the requirement to expend a large amount of energy and footprint on chips that are contributing very little compute performance to the system. It's a problem that has led to an explosion of interest in the use of low-power ARM CPUs to sit alongside the co-processor boards, and one that Intel plans to neatly side-step altogether.

The company's previous PCIe-based Xeon Phi products have already enjoyed some high-profile wins, accounting for 13 of the world's fastest supercomputers as ranked in the latest TOP500 list - including the world's single fastest supercomputer, China's Tianhe-2, which features 16,000 nodes each with two Ivy Bridge-based Xeon CPUs and three Xeon Phi co-processor cards.

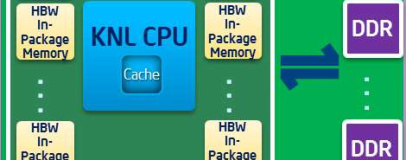

The new Xeon Phi chips will also include a combination of near and far memory, using what Intel dubs High-Bandwidth In-Package Memory (HBW IPM). This puts a chunk of rapidly-addressable memory on the same package as the Knights Landing CPU but separate from the on-die cache memory which holds the most commonly-accessed data. Large quantities of traditional DDR-based memory are then placed on the motherboard as usual. Thus far, Intel has not detailed exactly how much HBW IPM the first Knights Landing Xeon Phi boards will have - but expect it to be a significant amount compared to the relative paucity of cache memory typical to modern processors.

Intel has also promised to offer customised versions of the Knights Landing CPUs, working with partners - much as AMD has with Microsoft and Sony on their next-generation console chips - to tweak the design for individual requirements.

While GPUs still account for the overwhelming majority of co-processor accelerators in the supercomputing market, it's clear that Intel isn't willing to give up the fight - and with its highly-compatible x86 architecture, it seems almost certain that work carried out for the supercomputer and HPC market on many-core Xeon Phi CPUs will some day trickle down to the desktop and lead to a highly parallel future for all.

Designed to combat the growing trend for supercomputing and other high-performance customers to turn to graphics processing units-based accelerator boards like Nvidia's Tesla family for highly-parallel workloads, Xeon Phi is the first commercial product from Intel's Many Integrated Cores (MIC) project. Based on an x86 architecture roughly equivalent to the original Pentium, the first Xeon Phi is an add-in PCI Express card offering more than 50 processing cores and a stack of high-speed memory for highly parallel tasks.

According to details released by Intel at the Supercomputing Conference late yesterday, however, it won't always be this way. The next-generation version will also be available as a standalone CPU, constructed on a 14nm process node. Unlike the original Xeon Phi, the next-generation model will be able to operate entirely independently - executing both serial operating system tasks and parallel code on the same chip - with no need for a traditional CPU at all.

That's something that is likely to make the HPC market sit up and take notice. Traditional highly-parallel co-processing boards, whether GPU or CPU based in architecture, rely on having traditional processors to handle running the operating system and keeping the accelerators fed with data. This leads to the requirement to expend a large amount of energy and footprint on chips that are contributing very little compute performance to the system. It's a problem that has led to an explosion of interest in the use of low-power ARM CPUs to sit alongside the co-processor boards, and one that Intel plans to neatly side-step altogether.

The company's previous PCIe-based Xeon Phi products have already enjoyed some high-profile wins, accounting for 13 of the world's fastest supercomputers as ranked in the latest TOP500 list - including the world's single fastest supercomputer, China's Tianhe-2, which features 16,000 nodes each with two Ivy Bridge-based Xeon CPUs and three Xeon Phi co-processor cards.

The new Xeon Phi chips will also include a combination of near and far memory, using what Intel dubs High-Bandwidth In-Package Memory (HBW IPM). This puts a chunk of rapidly-addressable memory on the same package as the Knights Landing CPU but separate from the on-die cache memory which holds the most commonly-accessed data. Large quantities of traditional DDR-based memory are then placed on the motherboard as usual. Thus far, Intel has not detailed exactly how much HBW IPM the first Knights Landing Xeon Phi boards will have - but expect it to be a significant amount compared to the relative paucity of cache memory typical to modern processors.

Intel has also promised to offer customised versions of the Knights Landing CPUs, working with partners - much as AMD has with Microsoft and Sony on their next-generation console chips - to tweak the design for individual requirements.

While GPUs still account for the overwhelming majority of co-processor accelerators in the supercomputing market, it's clear that Intel isn't willing to give up the fight - and with its highly-compatible x86 architecture, it seems almost certain that work carried out for the supercomputer and HPC market on many-core Xeon Phi CPUs will some day trickle down to the desktop and lead to a highly parallel future for all.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.