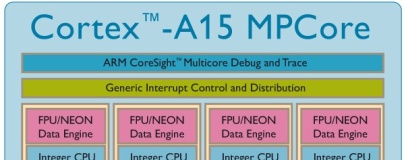

British chip giant ARM has announced a new hard macro implementation of its Cortex-A15 system-on-chip processor, which hits three milestones at once: it's the company first hard macro to feature quad-cores, the Cortex-A15 IP and to be based on a 28nm process size.

In system-on-chip design, there are two main methodologies: soft macro and hard macro. In the former, the design isn't tied to any particular manufacturing process. Instead, the design is provided to customers in the form of Register Transfer Level (RTL) code. From there, it's up to the customer to decide how the chip should be made - offering licensees the maximum flexibility.

Hard macro IP, by contrast, is provided as a block-level design with a specific manufacturing process in mind. Hard macro IP is typically optimised for performance, power consumption, timing or footprint, but comes with the downside of reduced flexibility: two processors made by two different companies but based on the same hard macro IP will, by and large, be indistinguishable in terms of features and performance.

The main advantage of hard macro design is in time-to-market. Where a company would have to spend time optimising the soft macro design for their own requirements - with errors at this point proving extremely costly - a hard macro customer can simply build the chips immediately.

'For SoC designers looking to make a trade-off between the flexibility offered by the traditional RTL-based SoC development strategy and a rapid time to market, with ensured, benchmarked power, performance and area, an ARM hard macro implementation is an ideal, cost-effective solution,' claimed ARM's Jim Nicholas at the product launch. 'This new Cortex-A15 hard macro is an important addition to our portfolio and will enable a wider array of partners to leverage the outstanding capabilities of the Cortex-A15 processor.'

ARM's latest hard macro release is important for a number of reasons: first and foremost, it's the first to be designed with the 28nm process size in mind - giving hard macro licensees the ability to compete with the big boys like Samsung and Nvidia for the first time.

Secondly, it's the company's first quad-core hard macro. With hard macro IP now available, smaller companies will be able to build their own quad-core implementations - meaning we can expect to see an explosion in quad-core tablets and smartphones over the coming months.

Finally, it's the first hard macro to feature the ARMv7-based Cortex-A15 'Eagle' IP. Unlike ARM's previous chips, the Cortex-A15 boasts a wealth of impressive functionality which makes it suitable for use outside the traditional embedded and mobile markets. Support for greater than 4GB of RAM and hardware virtualisation technologies indicates ARM's desire to attack the microserver and cloud computing markets, although at present the chip is still a 32-bit part - albeit one with 48-bit memory addressing.

The particular design announced by ARM ahead of its formal unveiling at the Cool Chips conference today boasts a 2GHz clock speed, a pair of 32KB L1 caches - shared between two cores - and a single shared 2MB L2 cache, 224 interrupts, six power domains, and support for the AMBA protocol for on-chip interconnections in multi-processor implementations.

For Intel, the announcement is a reminder that ARM is serious about its slow but steady march into the datacentre. While Intel's rival low-power Atom parts are seeing a small up-take in the server market, there's no doubt that ARM poses a real threat to one of Intel's most profitable industries.

In system-on-chip design, there are two main methodologies: soft macro and hard macro. In the former, the design isn't tied to any particular manufacturing process. Instead, the design is provided to customers in the form of Register Transfer Level (RTL) code. From there, it's up to the customer to decide how the chip should be made - offering licensees the maximum flexibility.

Hard macro IP, by contrast, is provided as a block-level design with a specific manufacturing process in mind. Hard macro IP is typically optimised for performance, power consumption, timing or footprint, but comes with the downside of reduced flexibility: two processors made by two different companies but based on the same hard macro IP will, by and large, be indistinguishable in terms of features and performance.

The main advantage of hard macro design is in time-to-market. Where a company would have to spend time optimising the soft macro design for their own requirements - with errors at this point proving extremely costly - a hard macro customer can simply build the chips immediately.

'For SoC designers looking to make a trade-off between the flexibility offered by the traditional RTL-based SoC development strategy and a rapid time to market, with ensured, benchmarked power, performance and area, an ARM hard macro implementation is an ideal, cost-effective solution,' claimed ARM's Jim Nicholas at the product launch. 'This new Cortex-A15 hard macro is an important addition to our portfolio and will enable a wider array of partners to leverage the outstanding capabilities of the Cortex-A15 processor.'

ARM's latest hard macro release is important for a number of reasons: first and foremost, it's the first to be designed with the 28nm process size in mind - giving hard macro licensees the ability to compete with the big boys like Samsung and Nvidia for the first time.

Secondly, it's the company's first quad-core hard macro. With hard macro IP now available, smaller companies will be able to build their own quad-core implementations - meaning we can expect to see an explosion in quad-core tablets and smartphones over the coming months.

Finally, it's the first hard macro to feature the ARMv7-based Cortex-A15 'Eagle' IP. Unlike ARM's previous chips, the Cortex-A15 boasts a wealth of impressive functionality which makes it suitable for use outside the traditional embedded and mobile markets. Support for greater than 4GB of RAM and hardware virtualisation technologies indicates ARM's desire to attack the microserver and cloud computing markets, although at present the chip is still a 32-bit part - albeit one with 48-bit memory addressing.

The particular design announced by ARM ahead of its formal unveiling at the Cool Chips conference today boasts a 2GHz clock speed, a pair of 32KB L1 caches - shared between two cores - and a single shared 2MB L2 cache, 224 interrupts, six power domains, and support for the AMBA protocol for on-chip interconnections in multi-processor implementations.

For Intel, the announcement is a reminder that ARM is serious about its slow but steady march into the datacentre. While Intel's rival low-power Atom parts are seeing a small up-take in the server market, there's no doubt that ARM poses a real threat to one of Intel's most profitable industries.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.