ARM, Xilinx, Cadence, TSMC announce 7nm CCIX test chip plan

September 12, 2017 | 10:36

Companies: #arm #cadence #taiwan-semiconductor #tsmc #xilinx

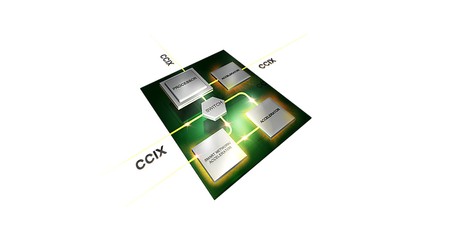

ARM, Xilinx, Cadence, and Taiwan Semiconductor (TSMC) have jointly announced plans to produce the first test chip for the Cache Coherent Interconnect for Accelerators (CCIX) project, which aims to prove that many-core ARM processors linked to field-programmable gate arrays (FPGAs) have a home in high-performance computing.

The concept behind the Cache Coherent Interconnect for Accelerators (CCIX) project is simple yet promises a paradigm shift in computing: A CCIX chip, the companies claim, would allow developers to access and process data wherever in the system it resides without relying on any complex programming environments. Using existing server interconnect infrastructure, CCIX is claimed to offer higher bandwidth, lower latency, and the ability to easily share memory - including cache - between processors.

Each company delivers their own technology to the project: The test vehicle is to be built on TSMC's 7nm FinFET process node, will include ARM processor cores based on the company's DynamIQ many-core technology, CMN-600 coherent on-chip bus, and base intellectual property (IP), with Cadence-provided input-output, memory, and PCI Express technology plus the company's core CCIX IP, with connectivity to Xilinx Virtex UltraScale+ FPGAs via the CCIX chip-to-chip interconnect protocol.

'Artificial intelligence and deep learning will significantly impact industries including media, consumer electronics and healthcare,' claims Dr. Cliff Hou, TSMC vice president for the company's Research & Development/Design and Technology Platform division, of the project's goals. 'TSMC's most advanced 7nm FinFET process technology provides high performance and low power benefits that satisfy distinct product requirements for High-Performance Computing (HPC) applications targeting these markets.'

'With the surge in artificial intelligence and big data, we’re seeing increasing demand for more heterogeneous compute across more applications,' adds Noel Hurley, vice president and general manager for ARM's Infrastructure Group. 'The test chip will not only demonstrate how the latest ARM technology with coherent multichip accelerators can scale across the data centre, but reinforces our commitment to solving the challenge of accessing data quickly and easily. This innovative and collaborative approach to coherent memory is a significant step forward in delivering high-performance, efficient data centre platforms.'

'By building an ecosystem for high-performance computing with our collaboration partners, we will enable our customers to quickly deploy innovative new architectures at 7nm and other advanced nodes for these growing data centre applications,' concludes Babu Mandava, senior vice president and general manager of the IP Group at Cadence. 'The CCIX industry standard will help drive the next generation of interconnect that provides the high-performance cache coherency that the market is demanding.'

The CCIX project is far from the only industry attempt at cache-coherent collaboration between general-purpose processors and application-specific accelerators, of course: The AMD-led HSA Foundation launched back in 2012 with the same goal, though concentrating on collaboration between CPU and GPU hardware. ARM in the data centre has traditionally been a tough sell, too: Back in 2014 both Samsung and Nvidia confirmed they were dropping planned ARM-based data centre products, while AMD has done little with its ARM-based Opteron products since the 2014 launch of the Opteron A1100 Series developer kit.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.