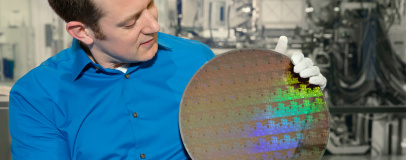

Computing giant IBM, in partnership with Samsung and GlobalFoundries, has announced what it claims is the first semiconductor process which provably scales down to 5nm, packing 30 billion transistors onto a fingernail-size chip.

While IBM's processing products are a less common sight than those of AMD, Intel, or ARM's multitudinous licensees, concentrating as it does on the data centre and high-performance computing markets, IBM itself has been expending considerable effort to keep up with the increasingly challenging demands of Moore's Law. Back in 2015, the company demonstrated the world's first FinFET chip based on a 7nm process, and now the company claims to have a means of producing the industry's first parts based on a 5nm process node.

'For business and society to meet the demands of cognitive and cloud computing in the coming years, advancement in semiconductor technology is essential,' explained Arvind Krishna, senior vice president of IBM's hybrid cloud division and director of IBM's Research arm. 'That’s why IBM aggressively pursues new and different architectures and materials that push the limits of this industry, and brings them to market in technologies like mainframes and our cognitive systems.'

Unveiled as part of the Symposia on VLSI Technology and Circuits conference in Kyoto, Japan and developed in partnership with Research Alliance member companies GlobalFoundries and Samsung, IBM's 5nm process makes use of stacks of silicon nanosheets to build up the device structure - a departure from the more mainstream FinFET design IBM used for its 7nm chips. According to the companies' testing, chips produced on a 5nm nanosheet process node can offer a 40 percent performance improvement at the same power envelope or 75 percent power savings with no loss of performance when compared to unnamed 'leading edge 10nm technology available in the market'.

IBM claims that the nanosheet system has other advantages over simply attempting to shrink current FinFET technology, too: The company has claimed that by continuous adjustment of the nanosheet width during production via extreme ultraviolet lithography (EUV) fine-tuning of power versus performance in specific circuits can be achieved, something it says is not possible with fixed-height FinFET.

While IBM describes the technology as 'not too far off in the future', none of the partner companies have yet announced a schedule for implementation and commercial exploitation.

While IBM's processing products are a less common sight than those of AMD, Intel, or ARM's multitudinous licensees, concentrating as it does on the data centre and high-performance computing markets, IBM itself has been expending considerable effort to keep up with the increasingly challenging demands of Moore's Law. Back in 2015, the company demonstrated the world's first FinFET chip based on a 7nm process, and now the company claims to have a means of producing the industry's first parts based on a 5nm process node.

'For business and society to meet the demands of cognitive and cloud computing in the coming years, advancement in semiconductor technology is essential,' explained Arvind Krishna, senior vice president of IBM's hybrid cloud division and director of IBM's Research arm. 'That’s why IBM aggressively pursues new and different architectures and materials that push the limits of this industry, and brings them to market in technologies like mainframes and our cognitive systems.'

Unveiled as part of the Symposia on VLSI Technology and Circuits conference in Kyoto, Japan and developed in partnership with Research Alliance member companies GlobalFoundries and Samsung, IBM's 5nm process makes use of stacks of silicon nanosheets to build up the device structure - a departure from the more mainstream FinFET design IBM used for its 7nm chips. According to the companies' testing, chips produced on a 5nm nanosheet process node can offer a 40 percent performance improvement at the same power envelope or 75 percent power savings with no loss of performance when compared to unnamed 'leading edge 10nm technology available in the market'.

IBM claims that the nanosheet system has other advantages over simply attempting to shrink current FinFET technology, too: The company has claimed that by continuous adjustment of the nanosheet width during production via extreme ultraviolet lithography (EUV) fine-tuning of power versus performance in specific circuits can be achieved, something it says is not possible with fixed-height FinFET.

While IBM describes the technology as 'not too far off in the future', none of the partner companies have yet announced a schedule for implementation and commercial exploitation.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.