Intel has made good on the name of its Architecture Day event by revealing a brand new CPU microarchitecture called Sunny Cove and outlining a new roadmap for future developments.

With Intel being long, long overdue to deliver 10nm-based CPUs in volume, it is now finally willing to share details on the ‘Architecture’ stage of its Process-Architecture-Optimisation (PAO) execution plan, including the fact that the first Xeon and Core CPUs using Sunny Cove will launch in 2019. If you stay up to date on Intel roadmaps, then firstly congratulations, as it’s not an easy task, and secondly you might be wondering where the Sunny Cove name has come from and what happened to Ice Lake i.e. the 10nm-based CPUs with a new architecture set to launch in 2019. The answer is we don’t know, as Intel would not be drawn into answering what any potential CPUs using Sunny Cove would be called, but it does seem likely that Sunny Cove will either be a new name for Ice Lake given the similarities or that Intel is starting a process of separating chip codenames from the microarchitecture inside them.

Before we get to Sunny Cove details, we should also point out that the Cannon Lake architecture was also conspicuous in how it was not mentioned at all. Cannon Lake is the highly troubled ‘Process’ element; the plan was to shrink 14nm Kaby/Coffee Lake designs down to the 10nm process, but thus far Cannon Lake has only appeared in a single Core i3 laptop CPU that was produced in very low volume and where the onboard graphics had been disabled. Intel may even be skipping Cannon Lake completely and moving straight to Sunny Cove/Ice Lake, thus violating the PAO plan by merging P and A, but the truth is we just don’t know right now.

While it remains to be seen how exactly the various Lakes and Coves will play out regarding final products, what we do know is that Sunny Cove will be a whole new architecture with design changes focused firstly on improving IPC (instructions per clock) in general purpose compute tasks and secondly in accelerating special purpose workloads in specific areas like AI and cryptography. Intel is not expecting to make any frequency headway with Sunny Cove, which shouldn’t come as a surprise given how much it has been forced to optimise its 14nm parts with clock speed increases as it tries to get 10nm right.

While not committing to any specific IPC increases other than saying they are ‘significant’, Intel has given a broad overview of a threefold approach to eking out the extra performance: Deeper, Wider, Smarter. And now we have Daft Punk stuck in our heads…

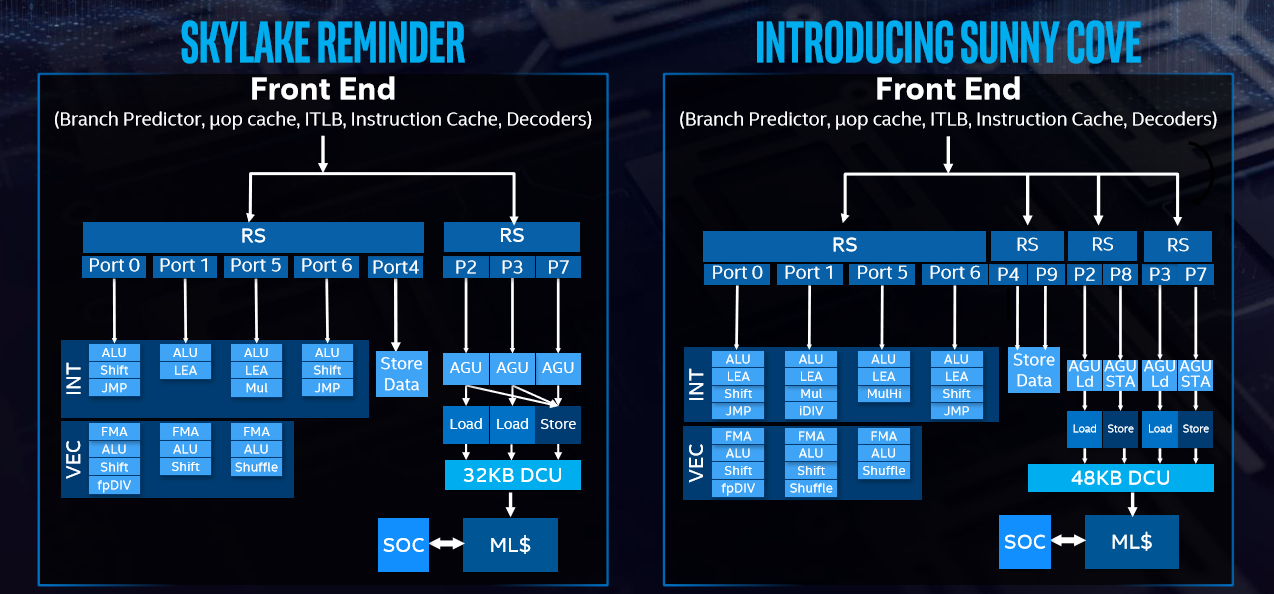

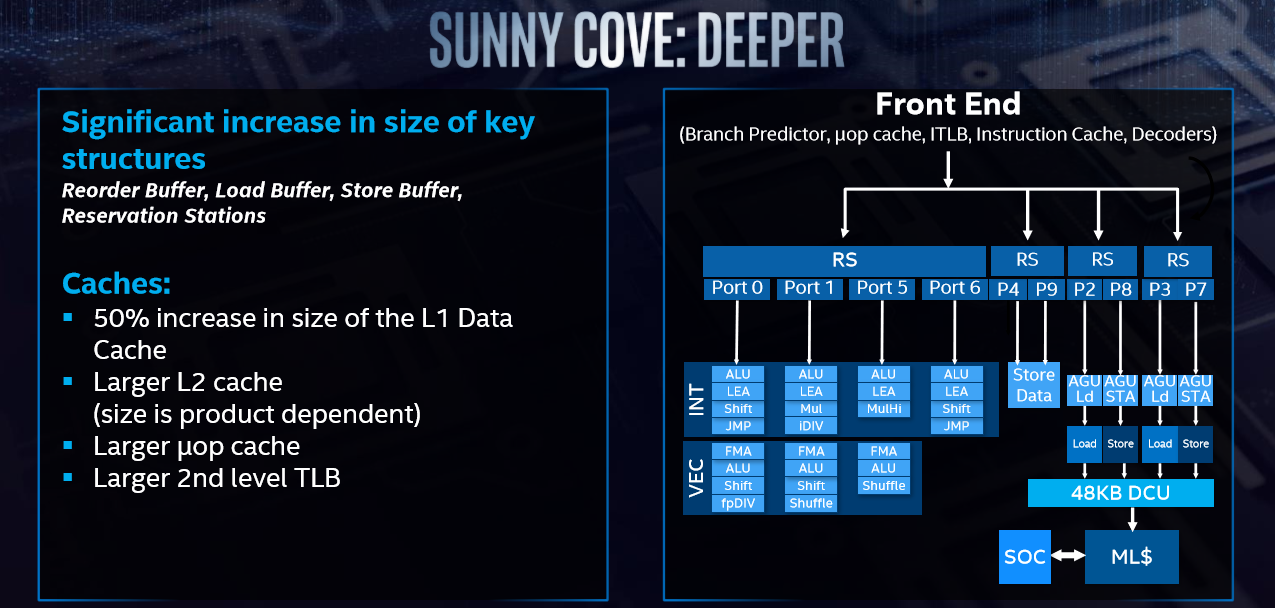

The Deeper part of the equation refers mostly to a series of size increases to various caches and structures. Perhaps most notable is a 50 percent increase in L1 cache from 32KB to 48KB, as this size has remained fixed for over a decade. L2 cache, micro-op cache, and various buffers also get bigger, and the overall result is the ability to have a larger set of instructions held on chip, allowing Intel to ‘look deeper’ and find more instructions than before that can be run independently within the same clock cycle.

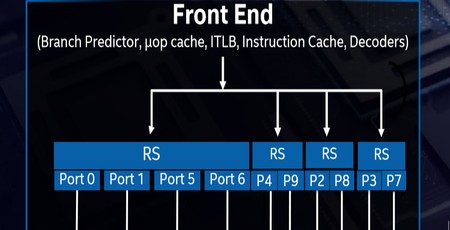

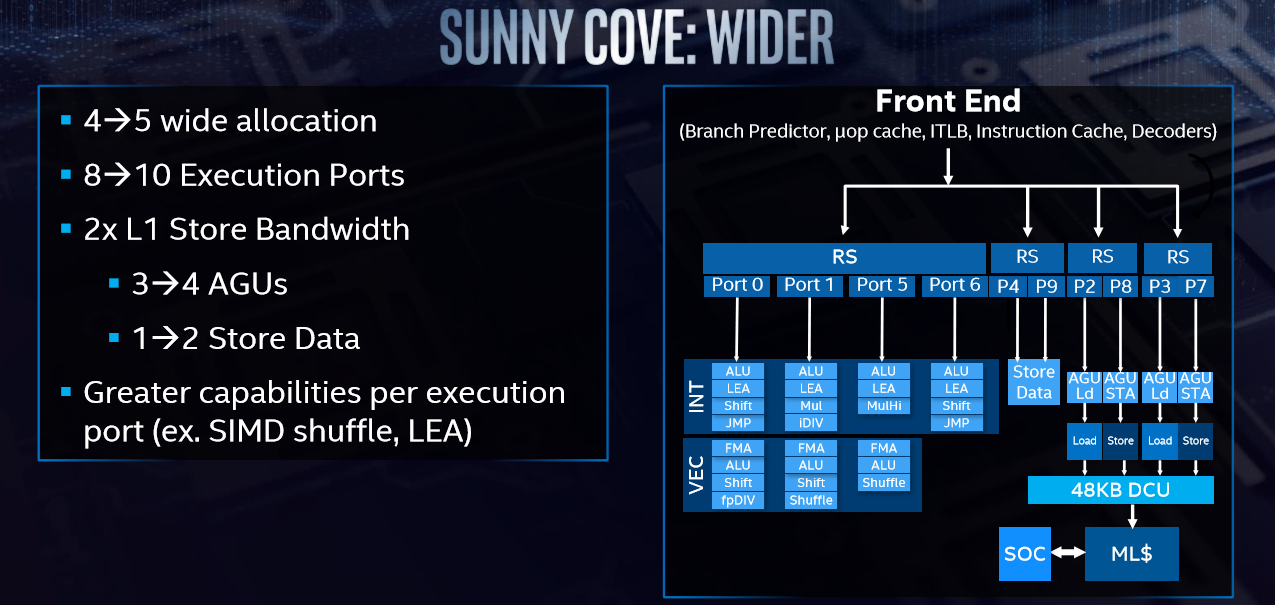

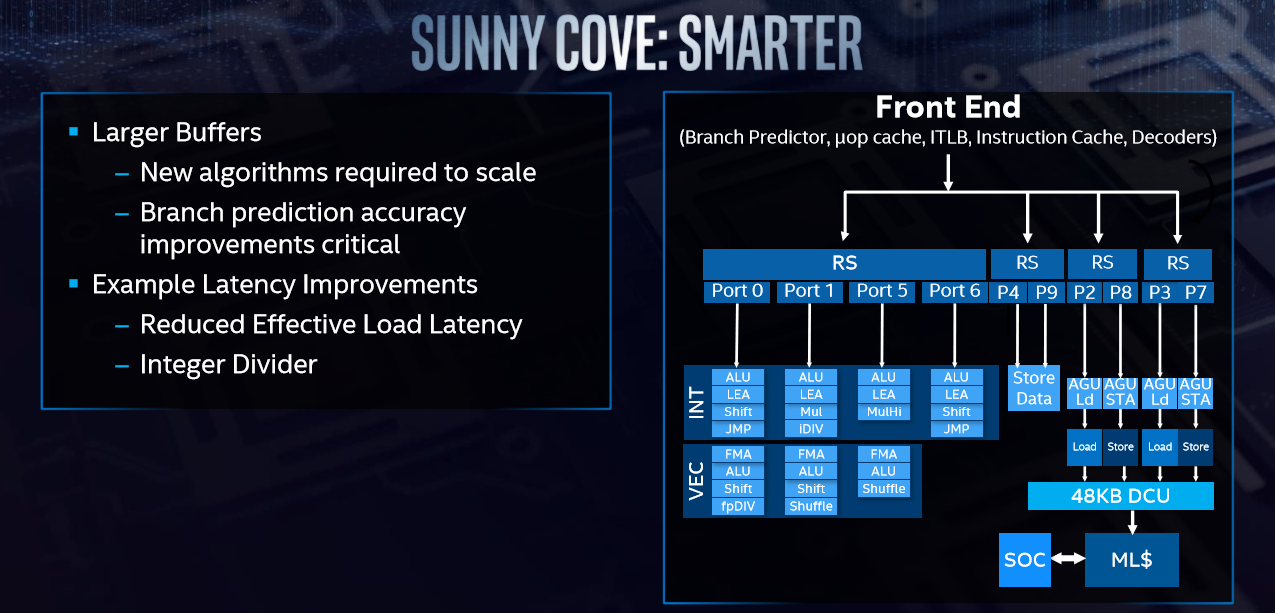

The second part, Wider, is common terminology and refers to a chip’s ability to execute more instructions in parallel by adding more execution units. In Sunny Cove, execution ports have gone from eight to 10 to facilitate this, and one key result is a doubling of L1 Store bandwidth. Extra capabilities have been added to the execution ports as well.

The third and final part of the Sunny Cove IPC equation is Smarter. While increasing execution units and improving cache and buffer sizes have obvious benefits, doing this changes the structure of the CPU and makes it more complex. As such, it’s necessary to develop more advanced algorithms than before in order maintain power efficiency in the new larger structure. Branch prediction is highlighted as a particularly important example, because with the CPU now picking out and running more instructions at once, branch mispredicts are more costly, as more instructions will need to be discarded. As such, the rate of of mispredicts needs to be lower. Intel also highlights a reduction in effective (not physical) load latency as a result of its Smarter work.

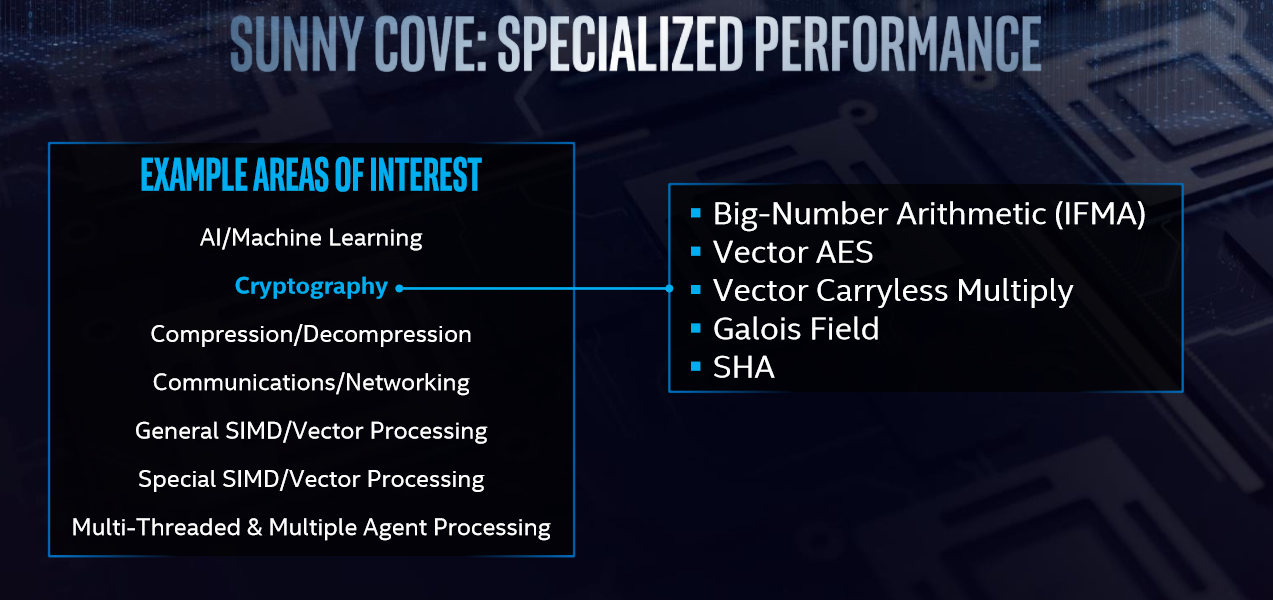

As well as general purpose compute improvements, Intel also revealed that Sunny Cove will feature specialised performance enhancements for specific use cases and algorithms via instruction set architecture (ISA) extensions.

On the topic of security, no new hardware-level mitigations against the various publicly known speculative side-channel attacks were announced, but Sunny Cove CPUs should at least incorporate the current include Variant 3 (Meltdown) and L1TF (AKA Variant 5) mitigations as well as Spectre Variation 2 mitigations being introduced with Cascade Lake server chips, with these latter ones also relying to a degree on operating system/virtual machine manager level mitigations too.

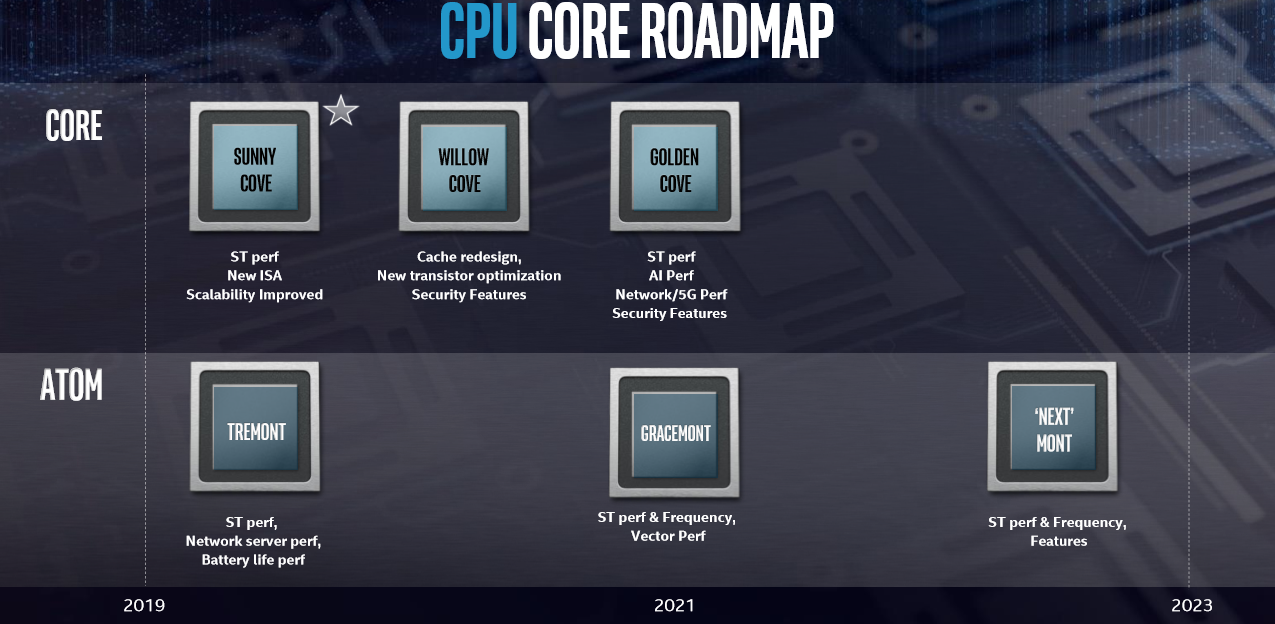

The Sunny Cove architecture is not the only new announcement, as Intel also confirmed Willow Cove and Golden Cove taking us to 2021. Again, exactly how this ties in with the existing Lake roadmap remains to be seen.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.