Intel has announced additional details regarding its next-generation Xeon Phi co-processor, Knights Landing, with the promise of up to three-fold performance increase over its predecessor at a lower power consumption.

Based on the research carried out by the company during its aborted Larrabee discrete graphics project, Xeon Phi is part of Intel's Many Integrated Core (MIC) programme. Designed to combat the growing popularity of accelerator boards from Nvidia and AMD in the high-performance computing (HPC) market, Xeon Phi offers up to fifty physical x86 processing cores in a mesh-style topography with access to fast GDDR5 memory. Using these cores, HPC customers can quickly port their software across for acceleration without the need to use an entirely new architecture like Nvidia's CUDA.

The current-generation Xeon Phi add-in board already powers the world's fastest supercomputer, China's Tianhe-2, but the Knights Landing successor promises to blow it out of the water. As well as coming in a socket format for the first time and being able to act as the only CPU in the system where the current add-in board requires a traditional CPU as well, the Knights Landing platform will showcase some of Intel's most bleeding-edge technologies.

According to an announcement made at the International Supercomputer Conference this week, Knights Landing will come with Intel's Omni-Scale Fabric technology embedded. A high-speed interconnect, OSF is integrated directly into the processor's package and allows for ultra-high-speed communications - key to shifting data to and from the processor's many cores efficiently, and a major source of the claimed three-fold performance boost promised by Intel. After launching on the Xeon Phi, Intel will put OSF into its 14nm mainstream Xeon chips and, inevitably, some variant of the technology will trickle down to the desktop in time.

'Knights Landing will be the first true many-core processor to address today's memory and I/O performance challenges,' claimed Intel's Charles Wuischpard at the event. 'It will allow programmers to leverage existing code and standard programming models to achieve significant performance gains on a wide set of applications. Its platform design, programming model and balanced performance makes it the first viable step towards exascale.'

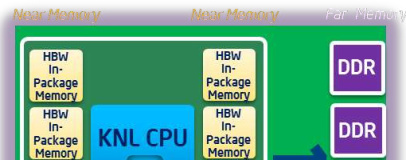

As well as OSF, the next-generation Xeon Phi chips will include up to 16GB of on-package through-silicon via (TSV) memory developed in partnership with Micron. The initial models will feature more than 60 processing cores based on the company's Silvermont architecture, with modifications designed to appeal to the HPC crowd, and boast more than three teraflops (trillion floating point operations per second) in total. The socketed version will be binary-compatible with current-generation Xeons, Intel has promised, meaning they can boot any existing operating system and run standard server applications without porting.

The first Knights Landing Xeon Phi parts are expected to ship in the second half of next year. Pricing has not been provided, but is likely to sit firmly at the 'if you have to ask' end of the spectrum.

Based on the research carried out by the company during its aborted Larrabee discrete graphics project, Xeon Phi is part of Intel's Many Integrated Core (MIC) programme. Designed to combat the growing popularity of accelerator boards from Nvidia and AMD in the high-performance computing (HPC) market, Xeon Phi offers up to fifty physical x86 processing cores in a mesh-style topography with access to fast GDDR5 memory. Using these cores, HPC customers can quickly port their software across for acceleration without the need to use an entirely new architecture like Nvidia's CUDA.

The current-generation Xeon Phi add-in board already powers the world's fastest supercomputer, China's Tianhe-2, but the Knights Landing successor promises to blow it out of the water. As well as coming in a socket format for the first time and being able to act as the only CPU in the system where the current add-in board requires a traditional CPU as well, the Knights Landing platform will showcase some of Intel's most bleeding-edge technologies.

According to an announcement made at the International Supercomputer Conference this week, Knights Landing will come with Intel's Omni-Scale Fabric technology embedded. A high-speed interconnect, OSF is integrated directly into the processor's package and allows for ultra-high-speed communications - key to shifting data to and from the processor's many cores efficiently, and a major source of the claimed three-fold performance boost promised by Intel. After launching on the Xeon Phi, Intel will put OSF into its 14nm mainstream Xeon chips and, inevitably, some variant of the technology will trickle down to the desktop in time.

'Knights Landing will be the first true many-core processor to address today's memory and I/O performance challenges,' claimed Intel's Charles Wuischpard at the event. 'It will allow programmers to leverage existing code and standard programming models to achieve significant performance gains on a wide set of applications. Its platform design, programming model and balanced performance makes it the first viable step towards exascale.'

As well as OSF, the next-generation Xeon Phi chips will include up to 16GB of on-package through-silicon via (TSV) memory developed in partnership with Micron. The initial models will feature more than 60 processing cores based on the company's Silvermont architecture, with modifications designed to appeal to the HPC crowd, and boast more than three teraflops (trillion floating point operations per second) in total. The socketed version will be binary-compatible with current-generation Xeons, Intel has promised, meaning they can boot any existing operating system and run standard server applications without porting.

The first Knights Landing Xeon Phi parts are expected to ship in the second half of next year. Pricing has not been provided, but is likely to sit firmly at the 'if you have to ask' end of the spectrum.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.