Micro Magic 64-bit RISC-V CPU runs at 5GHz on 1W

December 2, 2020 | 12:20

The Arm-based Apple M1 processor has caused quite a stir among enthusiasts, analysts and the IT industry in general. However it is no great shakes according to California-based Micro Magic, an outfit best known for its Electronic Design Automation (EDA) tools, which has been working on what it claims to be the world’s fastest 64-bit RISC-V core.

About a month ago Micro Magic demoed a 64-bit RISC-V core it had designed to the EETimes. The core achieved 5GHz and 13,000 CoreMarks at 1.1V. The demo core was running on an Odroid SBC. That is a definite milestone but usually a single Micro Magic core runs at 0.8V nominal to deliver 11,000 CoreMarks at 4.25GHz, while consuming only 200mW.

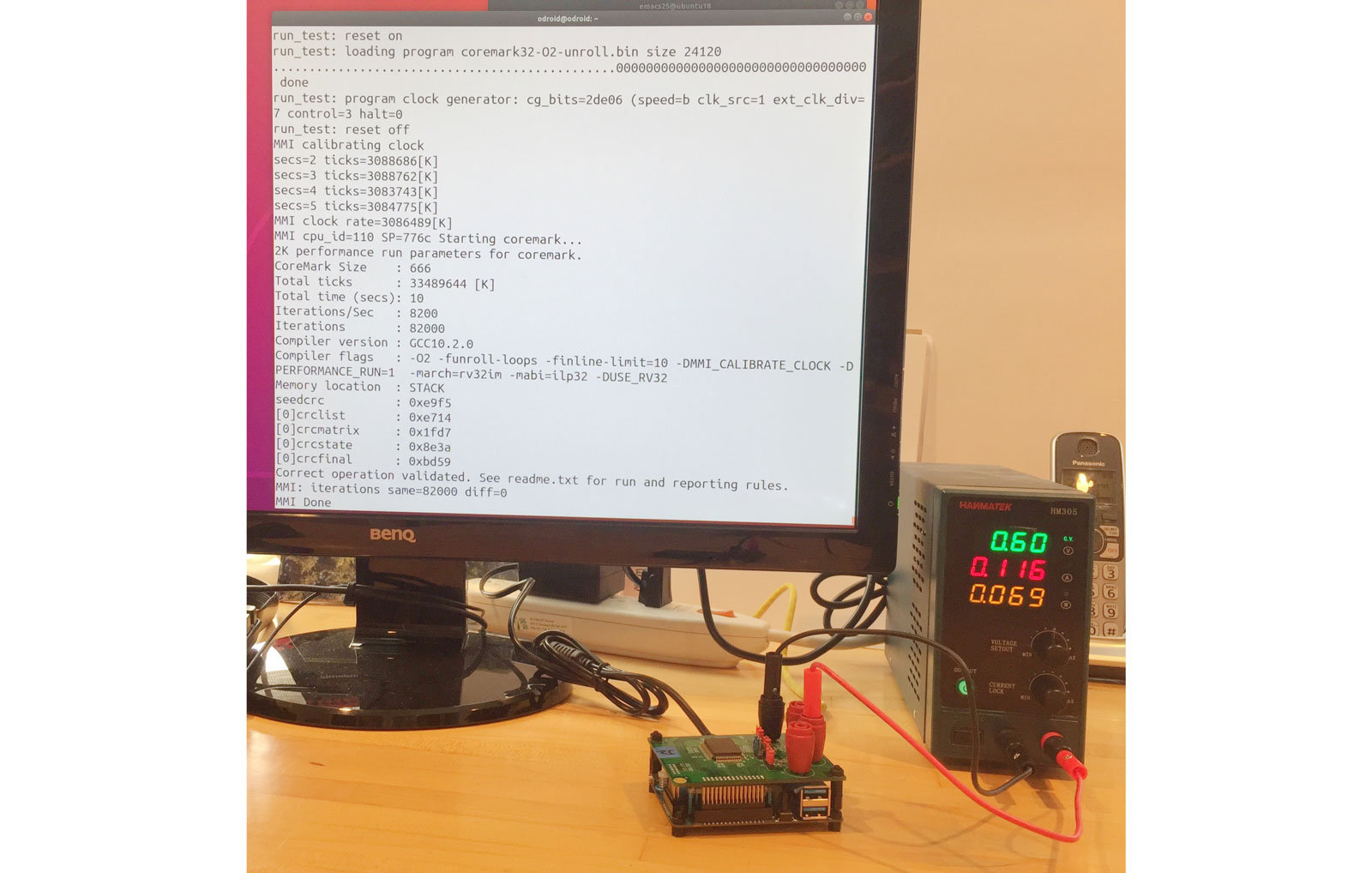

Micro Magic, Inc. RISC-V chip running at 3.08GHz consuming 0.69mW with a CoreMark score of 8,200.

Advisor to Micro Magic, Dr Andy Huang, provided some interesting comparisons between Micro Magic's RISC-V core, Apple's M1, and the fastest Arm reference design, the Cortex-A9. According to Huang, using the EEMBC benchmark, his RISC-V core achieves 55,000 CoreMarks per Watt. Meanwhile, a single Apple M1 core only scrapes 100 CoreMarks per Watt, and a single core from a Cortex-A9 processor can muster 1,112 CoreMarks per Watt. Thanks to the leading levels of efficiency one potential use of the RISC-V core could be in 25-core processors which have a power budget <5W.

Micro Magic was founded in 1995, was swallowed up by Juniper Networks and subsequently extricated itself in 2004. Founders, Mark Santoro and Lee Tavrow originally worked together at Sun Microsystems and led a team that developed a 300MHz SPARC microprocessor. Santoro also worked under Steve Jobs at Apple.

Any 'secret sauce' behind the design remains an erm... secret but Micro Magic's area of expertise, which usually makes its bacon, is in three-dimensional TSV (through silicon via) layout tools. This might provide a clue to the winning qualities of its 64-bit RISC-V design. Other clues come from Huang's claim to have implemented David Patterson's original vision for the reduced instruction set computer (RISC) architecture in as elegant way as possible.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.