Intel has released details of its first discrete graphics processing unit (GPU) since the abandonment of the Larrabee project, unveiling a block diagram for a 14nm prototype at the International Solid-State Circuits Conference (ISSCC) in San Francisco this week.

Back in 2007 Intel had visions of competing with AMD and Nvidia in the discrete high-performance GPU market, announcing the Larrabee GPU project with the promise of a 2008 unveiling. Sadly, while wafers, die photographs, and even live demos would follow, by late 2009 Intel would cancel its plans in favour of redirecting the research into the Many Integrated Core (MIC) co-processor initiative that would become the Xeon Phi server-centric product range.

Intel's poaching of AMD Radeon Technologies Group head Raja Koduri in November last year, though, brought with it the promise, again, of discrete graphics products - and Intel may have shown off its first effort on that front at the International Solid-State Circuits Conference (ISSCC) this week.

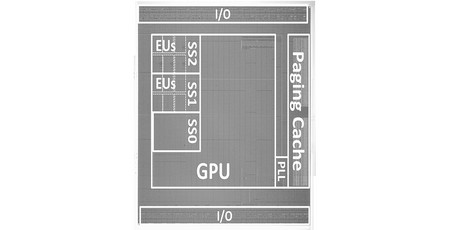

As part of a scheduled presentation titled 'An Energy Efficient Graphics Processor Featuring Fine-Grain DVFS with Integrated Voltage Regulators, Execution-Unit Turbo, and Retentive Sleep in 14nm Tri-Gate CMOS', Intel has demonstrated its first discrete GPU prototype. While the slides from the presentation have not yet been made public, Japanese technology publication PC Watch has released copies which show a 14nm graphics processor based on a low-power variant of Intel's ninth-generation graphics processing technology with two clusters of execution units (EUs) on an 8mm² die with 1.5 billion transistors.

Raw performance, though, does not appear to be Intel's primary aim. As the presentation title suggests, the company is working on reducing the power required by discrete graphics with fine-grained voltage and frequency controls through the use of per-block integrated voltage regulators (IVR). According to Intel's presentation, this can result in an average power saving of 29 percent when the card is in its Turbo performance mode.

Intel, for its part, has not yet announced when - or, indeed, if - it plans to bring its prototype, which currently relies on an expensive and energy-inefficient field-programmable gate array (FPGA) for its glue logic, to production.

UPDATE 20180221:

Intel has issued a statement denying that the hardware on show at ISSCC represents a glimpse at its promised discrete graphics products. 'Last week at ISSCC, Intel Labs presented a research paper exploring new circuit techniques optimised for power management,' an Intel spokesperson has clarified. 'The team used an existing Intel integrated GPU architecture (Gen 9 GPU) as a proof of concept for these circuit techniques. This is a test vehicle only, not a future product. While we intend to compete in graphics products in the future, this research paper is unrelated. Our goal with this research is to explore possible, future circuit techniques that may improve the power and performance of Intel products.'

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.