Intel has announced preliminary results of its partnership with the Industrial Technology Research Institute of Taiwan (ITRI) on next-generation memory architecture, resulting in the development of a new high-speed memory array design.

Intel and ITRI announced their partnership back in December 2011, working to improve both the performance and memory efficiency of dynamic memory (DRAM) as part of Intel's Ultrabook slim form-factor laptop project. The idea was to use ITRI's research know-how and Intel's access to fabrication facilities - and, let's not forget, near-limitless quantities of R&D cash - to develop next-generation memory architectures for mobile devices that would boost battery life considerably over current-generation parts.

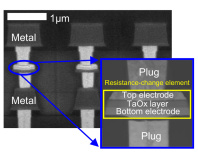

A year on, and that partnership is beginning to bear fruit: Intel's chief technology officer Justin Rattner held a press conference in Taipei earlier this week to announce the development of an experimental memory architecture. Sadly, Intel isn't quite ready to share the details, beyond the focus on interconnect technologies between memory cells and the use of an array-like structure.

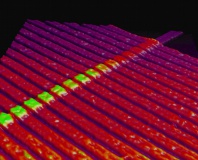

Even with such a small amount of detail, it's easy to make some educated guesses as to what Intel is working on: the company has already looked beyond planar transistor layouts with its tri-gate transistor technology, found in Ivy Bridge processors, and has partnered in the past on three-dimensional 'memory cube' systems. As a result, the ITRI memory architecture is likely to be based on a 2D grid-like array or even a 3D array, boosting data density and increasing inter-cell communication performance.

If so, Intel could have a winning technology on its hands: for server markets and high-performance computing, the new memory array architecture could promise significantly improved performance or capacity for the same power draw, while in mobile markets it could dramatically prolong battery life without harming the responsiveness of the device.

While Intel isn't giving away any details on the technology just yet, Rattner indicated that small-scale production had already begun with a view to trialling the system in consumer devices some time next year. Full-scale commercial exploitation, however, isn't expected to take place for another four years. With rival technologies including memristors, DFG-FET and SiO ReRAM heading to market in the near future, and Phase Change Memory already here, the company is going to have to be quick in order to steal a march on its rivals.

Intel and ITRI announced their partnership back in December 2011, working to improve both the performance and memory efficiency of dynamic memory (DRAM) as part of Intel's Ultrabook slim form-factor laptop project. The idea was to use ITRI's research know-how and Intel's access to fabrication facilities - and, let's not forget, near-limitless quantities of R&D cash - to develop next-generation memory architectures for mobile devices that would boost battery life considerably over current-generation parts.

A year on, and that partnership is beginning to bear fruit: Intel's chief technology officer Justin Rattner held a press conference in Taipei earlier this week to announce the development of an experimental memory architecture. Sadly, Intel isn't quite ready to share the details, beyond the focus on interconnect technologies between memory cells and the use of an array-like structure.

Even with such a small amount of detail, it's easy to make some educated guesses as to what Intel is working on: the company has already looked beyond planar transistor layouts with its tri-gate transistor technology, found in Ivy Bridge processors, and has partnered in the past on three-dimensional 'memory cube' systems. As a result, the ITRI memory architecture is likely to be based on a 2D grid-like array or even a 3D array, boosting data density and increasing inter-cell communication performance.

If so, Intel could have a winning technology on its hands: for server markets and high-performance computing, the new memory array architecture could promise significantly improved performance or capacity for the same power draw, while in mobile markets it could dramatically prolong battery life without harming the responsiveness of the device.

While Intel isn't giving away any details on the technology just yet, Rattner indicated that small-scale production had already begun with a view to trialling the system in consumer devices some time next year. Full-scale commercial exploitation, however, isn't expected to take place for another four years. With rival technologies including memristors, DFG-FET and SiO ReRAM heading to market in the near future, and Phase Change Memory already here, the company is going to have to be quick in order to steal a march on its rivals.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.