More Core:

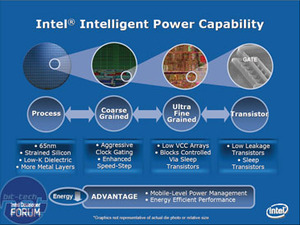

Intelligent Power Capability:Intel's mobile processors have included Speedstep technology of some description for some time now, and more recently in Intel's desktop line up. This is a technology that dynamically reduces the processor's operating speed if it is sitting idle, thus increasing battery life. While battery life isn't important in the desktop arena, power usage is becoming more and more important.

The Pentium 4 was a power hungry beast, so it required power management features to keep the power consumption numbers sensible. Core has further advanced Intel's Speedstep technology with a very fine controller that is capable of enabling parts of the processor when they are needed.

In fact, the technology is capable of shutting down one core altogether if you're only running a single-threaded application. Fast-switching transistor gates allow this to be achieved without affecting performance.

Advanced Smart Cache:

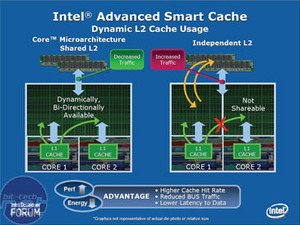

In Core, Intel has souped up its prefetch algorithms. These algorithms decide what data the processor needs to work on at a given point in time and then goes to collect the data from the memory controller before it is needed. This means that when the processor needs a certain piece of data, that data is already in the chip's high speed on-board L2 cache. This reduces the amount of traffic passing across the memory bus, because it is making more reads from L2 cache than it is from system memory.

To further reduce memory accesses, the Core architecture utilises an Advanced Smart Cache that allows both cores to share data stored in the L2 cache via an arbitration bus unit embedded in the cache. The technology dynamically allocates cache space between the two cores, minimising bus traffic by allowing both cores to access one copy of data, rather than allocating cache for the same data on a dual-core processor with independent L2 cache.

Smart Memory Access:

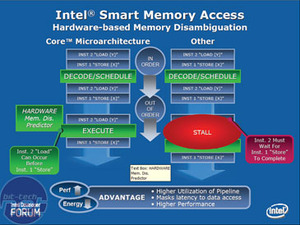

Along with this, Intel has also added a feature called memory disambiguation. Simply put, this feature helps to improve the processor's efficiency by enabling the chip to intelligently re-order instructions to reduce execution time. The algorithm makes an educated guess about whether or not the chip can move on to the next set of instructions - if it is right, the pipeline is filled and instructions are executed. If it turns out to be wrong, it just waits for the previous instruction to finish and then tries to execute again.

Advanced Digital Media Boost:

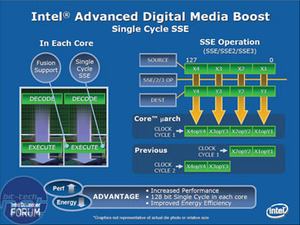

SSE instructions are an extension of the standard x86 instruction set. They are designed to replace the standard set of x86 instructions with more efficient SSE instructions that carry out the same task with less CPU overhead. Typically, SSE instructions are utilised in multimedia encoding, decoding, image manipulation and encryption - typical processor intensive tasks.

Core has introduced the ability to process 128-bit SSE instructions in a single clock cycle in either core. Previous Intel processors had only been able to handle half of a 128-bit SSE instruction in one clock cycle, meaning that it would take two clock cycles to execute one SSE instruction. If instruction lengths were short, the NetBurst architecture really suffered, as it would have to work its way through Intel's 31-stage pipeline twice. This effectively means we're going to see double the SSE instruction throughput at the same clock speed.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.