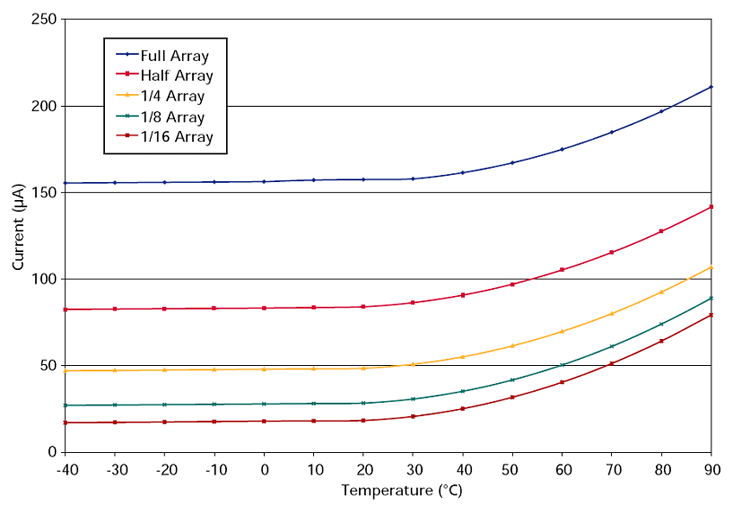

Different PASR configurations with distinctive Current levels

Source: Micron Technology

The self-refresh current falls when there are fewer arrays being refreshed but the current draw will automatically increase when the temperature becomes higher, because the array needs to be refreshed more frequently. This feature usually uses on-die thermal sensors embedded within the chip itself to ascertain its exact temperature.

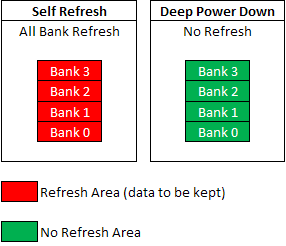

Deep Power Down (DPD)

In Deep Power Down mode, the internal power supply is switched off and the all refresh operations are suspended. As a result, data will not be retained after entering the DPD mode.Under normal operations, a single active bank will usually consume less the 80mA. When the refresh is active, the power consumption is about three times as much as during normal operation, however in DPD mode, the current use is reduced to about 10µA.

Overview of Self-Refresh and Deep Power Down modes

Source: Elpida Memory

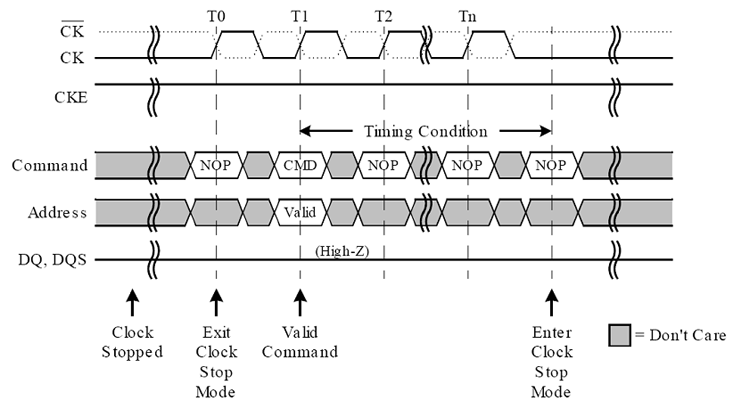

Clock Stop Mode

This feature increases power savings by having fewer transitions on the clock path. There are predominantly two methods used to achieve this according to Micron Technology:- Changing the clock frequency when the data transfers require a different rate of speed, or,

- Holding CKE HIGH, with CK LOW and CK HIGH for the full duration of Clock Stop Mode

According to JEDEC, the clock can even be stopped completely under the following conditions:

- The last command (ACTIVE, READ, WRITE, PRECHARGE, AUTO REFRESH or MODE REGISTER SET) has executed to completion, including any data-out during read bursts; the number of clock pulses per access command depends on the device’s AC timing parameters and the clock frequency.

- The related timing conditions (tRCD, tWR, tRP, tRFC, tMRD) have been met.

- CKE is held High.

Clock Stop Mode Entry and Exit

Source: JEDEC

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.