Foreword

by Richard SwinburneRyan Leng is an independent technology consultant and auditor for corporations in computer systems involving hardware, software, networking, security, IT policy formulation and training.

Originally trained in Computer Science and Economics, he has since worked in many fields relating to computer hardware integration, software design and engineering, surveillance systems, advertising, multimedia production, user-Interface engineering and graphic designs.

Ryan approached bit-tech with his unpublished book on DDR technology a short while ago, and when we read it we were greatly impressed with the depth and attention to detail, as well as being able to convey complex ideas in an easy to understand manner.

Whether you are adept in the knowledge of memory technology, it’s still an interesting read for a fundamental part of the PC’s architecture. We’ve cut his work up into several parts and this is the fourth article in the series.

For those that didn’t read Ryan’s first three articles on memory technology we highly recommend that you do, but don't fret if you haven't got the time to read them, because you don't need them to enjoy today's material.

DDR3

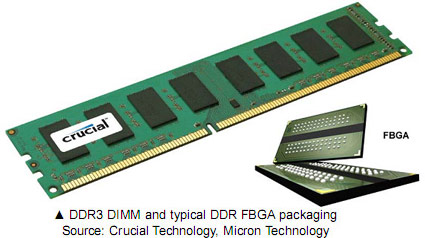

The third generation of DDR memory modules (DDR3) for desktop computers was first introduced, albeit in a limited amount, in the middle of 2007. Just like DDR2, the desktop DIMMs use a 240-pin connection interface, and the only noticeable visual difference between DDR2 and DDR3 modules is the DIMM’s Key-Notch location.

Almost all DRAMs used on desktop DDR3 modules will be based on Fine-pitch Ball Grid Array (FBGA) packaging and they are either square or slightly rectangular depending on the manufacturer. The FBGA package can actually accommodate more pins than are actually required – for this reason, some of the features that had been requested by designers and engineers for a long time, including things like Asynchronous RESET, were finally approved by JEDEC and made a part of the specification.

While many DDR3 DRAMs are based on 95nm fabrication technology, Micron’s 78nm process was transferred from its DDR2 D9 series into DDR3. Brett Williams, Senior Marketing Manager for Computing at Micron Technology recently informed us that Micron’s 65nm fabrication has been trailed and will be available very soon for DDR3. While this process should be available this year, by the end of DDR3’s life cycle we should expect to see a more refined fabrication technology closer to 45nm level.

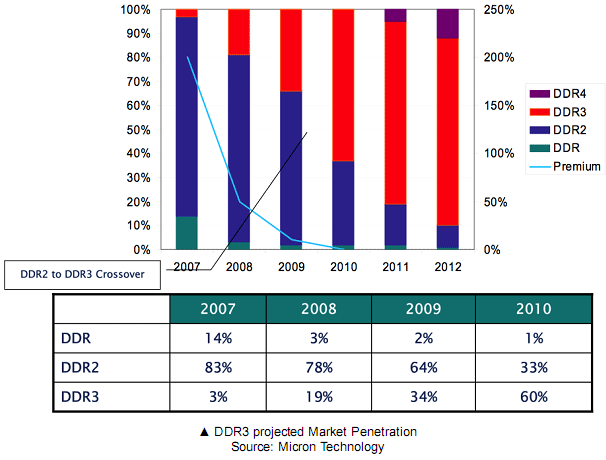

The 50 percent market share crossover point from DDR2 to DDR3 is anticipated to be some time in the first half of 2009 according to Micron Technology and even the significant ramp up in production in DDR3 from all major DRAM manufacturers is not anticipated until Q308 at the earliest, but more likely towards the end of 2008.

This will cause prices to remain high until 2009, at least in respect to the density and cost of DDR2. Performance module manufacturers like OCZ, Corsair and Super Talent have already made announcements of DDR3 modules performing in excess of 1.8-2GHz, going well beyond the JEDEC upper standard of 1.6GHz.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.