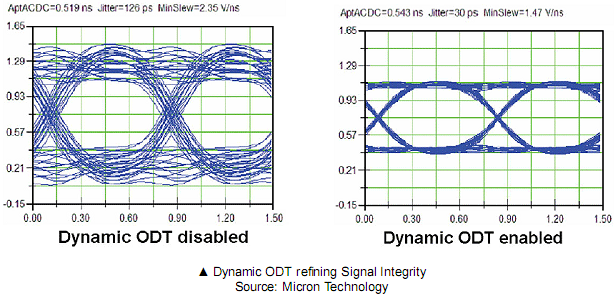

Dynamic On-Die Termination (ODT)

DDR3 extended DDR2’s On-Die Termination design by adding additional flexibility to optimise termination values for different conditions by acting as a way to manage the termination power consumption.A memory module that is not being accessed during a read or write operation can terminate the data bus with a low-impedance value of 30 or 40 ohms. During a write operation, the optimal termination can be changed to a high-impedance value of about 60 or 120 ohms.

According to Todd Farrell from Micron, “Dynamic ODT allows a DDR3 SDRAM device to change termination values seamlessly between write commands issued to different modules. This feature is not available in DDR2 SDRAM systems, which require a bus idle time when changing termination values on the same device.”

With dynamic ODT, the signal integrity is improved further by reducing interfering noise to a more manageable level by catering the termination values to different situations. This allows the memory to operate at a higher rate when compared to DDR2.

ZQ Driver Self-Calibration

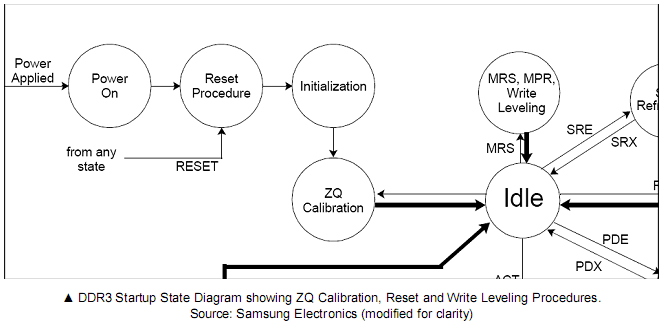

This feature is sometimes known as “ZQ Calibration” and was designated for enhanced calibration of the impedance values with tighter tolerances. It is an important improvement that involves the assignment of the so called “ZQ” pin for On-Chip Driver calibration functionality. The ZQ pin is located on the DRAM chip itself, hence can sometimes be referred to as the “ZQ Ball” in reference to the Ball-Grid Array (BGA) packaging.The ZQ Calibration operates at two levels: firstly, it is used during the start-up sequence before any major memory operation – this is known as “ZQ Calibration Long” or ZQCL. The start-up calibration generally takes longer and precedes DDR3 Write Levelling.

The second ZQ Calibration is known as a “ZQ Calibration Short” or ZQCS. It is sometimes referred to as “Tracking Calibration” as it takes place throughout the memory operation cycles but requires less time than the one in the start-up phase.

Tracking Calibration was implemented to reduce the possibility of severely inaccurate signal timing at a higher frequency, throughout the memory operations. By re-calibrating the impedance values during normal operation as the voltage and temperature drifts up and down, the problem of impedance discontinuity is significantly reduced.

To summarise, ZQCS continuously tracks and compensate for variations in voltage and temperature (PVT) to allow for the best Data Eye, and therefore the best Data transmission. The ZQ pin is linked to a highly precise external resistor, which is used for high definition adjustments of the “On” impedance of output drivers and ODT impedances.

ZQ Calibration is an important feature for DDR3: as more data is being squeezed in over a given time for faster transfer, DDR3 has smaller margins to work with. Without ZQ Calibration DDR3 will not be anywhere near as reliable.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.