AMD's Phenom II X4 940 and 920

Manufacturer AMDPhenom II X4 940

UK Price (as reviewed): TBAUS Price (as reviewed): $275 MSRP

Phenom II X4 920

UK Price (as reviewed): TBAUS Price (as reviewed): $235 MSRP

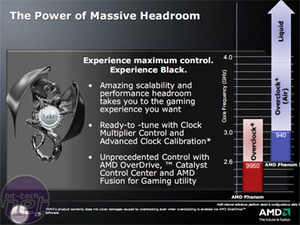

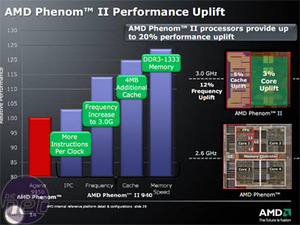

AMD's 45nm CPUs have arrived and while some might claim "better late than never" seeing as Intel has been shipping its own for more than a year now, the rest of us might be pleased they have arrived at all, given the recent struggles inside the company. The company's 45nm silicon on insulator (SOI) process allows for cooler CPUs, which affords AMD more thermal overhead for larger caches and higher clock speeds.

The latter, in particular, was AMD's single biggest problem with the 65nm Phenoms - the other "issue" was the limited overclocking and that caused enthusiasts to shy away and invest in Intel instead. This time around though, AMD claims its 45nm CPUs have a much greater performance overhead. So two out of two - good going so far!

The 45nm SOI fabrication process is slightly different to Intel's High-k Metal Gate which uses newer, alternative materials and was the biggest change in transistor technology since the 60s. In contrast, AMD's SOI technology stems on from its 65nm SOI process.

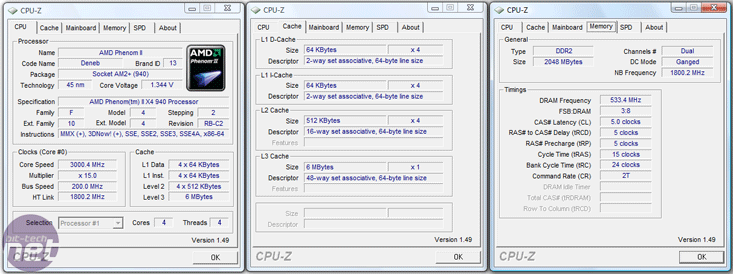

Phenom II AM2+ CPU Details

- Core Clock:

- 940: 3.0GHz

- 920: 2.8GHz

- 940: 3.0GHz

- L1 Cache: 64KB L1 data, 64KB L1 instruction per core, exclusive

- L2 cache: 512KB per core, exclusive

- L3 cache: 6MB accessible by all cores

- Hyper Transport and Northbridge Frequency:

- 940 and 920: 1.8GHz (3.6MT/s) HT 3.0 16-bit bi-directional

- 128-bit dual channel or two 64-bit single channels DDR2-1,066MHz

- ~758 Million transistors, 258mm² die size

- 940 and 920 TDP: 125W

These CPUs are AM2+ meaning DDR2 only, however AM3 arrives in February and supports both DDR2 and DDR3. The DDR2 memory controller on the Phenom II CPUs has been upgraded though to including an adaptive prefetch scheme which adjusts the prefretching depth depending on the buffer space available, effectively better making use of available resources by allowing for more chances to have the data needed ready to use locally. To aid this, there's also a "Coherent DRAM Prefetch" function that allows the memory controller to generate probes for DRAM prefetch requests too.

Bigger Cache

In terms of cache, the L1 and L2 cache sizes remain the same as the original Agena-based Phenom chips, but the L3 cache size has increased from 2MB to 6MB on the 45nm Phenom II. In conjunction with this, there has been a 50 percent increase in cache associativity from 32 to 48-way and also a two-cycle latency improvement. The latency improvement is dependent on cache frequency however, and this has been dropped from 2.0GHz on the 9850 and 9950 Phenom X4s to 1.8GHz in both Phenom IIs.The larger L3 cache might be a power consumption concern, however the sub cache sections can be stopped periodically when not in use in order to reduce power consumption. The caches are still exclusive, meaning L1, L2 and L3 are all kept separate for more cache space, but this also means each core has to snoop others for data rather than just probe L3.

AMD has doubled the core snoop bandwidth with its Phenom II processor and also allowed the L1 and L2 core caches to be copied to the 6MB L3 cache when they each drop into the ACPI C1 idle state. This means they only need to wake for their own thread execution duty and not cache snoops from other active cores.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.