This week, we've heard all about the new Core microarchitecture from Intel. But what exactly is Core? More to the point, what exactly is a microarchitecture? Having spent the last two days with my head buried in white papers and PowerPoint slides, I hope to have the answer for you guys. Throughout the article, you'll see scattered illustrations from the papers I've been dissecting, for a little added technical insight. Read on...

There are also various proprietary extensions to x86, such as Intel's SSE series. These are designed to be instructions that are faster or more efficient than x86 at certain types of operations.

When the processor itself receives an x86 instruction, it splits out the instruction into micro instructions. How it splits them out will depend entirely on the microarchitecture of the chip. It splits down the instructions into simple CPU operations that are then executed, reassembled back into x86 instructions, then sent back to the programme.

Fundamentally, microarchitecture is the implementation of processor architecture in silicon.

At a simple level, if you have a very fast and efficient microarchitecture, you can process instructions faster. If you have a bad micro architecture, your CPU will be slower.

When Intel designed the NetBurst microarchitecture for the Pentium 4, it was designed to be a performance beast. It was designed to scale very well with clock speed, and to just keep chewing through instructions. This made it a great chip for its time, but now our performance needs have changed. Its great advantage - that it scaled with clock speed - is wiped out now that we've hit 4GHz and it scales no further. It's brute force meant it ran incredibly hot.

Today's requirements for chips are now really dictated by the mobile space. Laptop computers are becoming the most popular types of computers, and obviously, brute force, hot chips are no good for this type of computer. What matters is efficient battery life and efficient use of processing power. This is why the Pentium M was created. Rather than create a chip that had a massive clock speed, and featured all kinds of features for brute force performance, Pentium M was designed to be power efficient whilst retaining high performance. It turns out that this is a fantastic way to design desktop chips too, which is why the spirit of Pentium M has very much inspired the design of the next-generation of Intel chips, based on Core.

Performance = Frequency x Instructions per Clock Cycle.

The equation shows that performance can be improved by increasing frequency, IPC or both. The P4 worked on frequency scaling: Core works on improving the number of IPCs and frequency scaling.

However, there's a third part of this pie, which is reducing the number of instructions needed, not just processed. If you can reduce the number of things the CPU has to calculate, then you effectively increase the number of IPCs. This is where things like SSE come in, improving on the x86 instruction set.

Despite the names, Intel's current 'new' chips - Core Duo and Core Solo - aren't based on the Core microarchitecture as such, although they have some similarities.

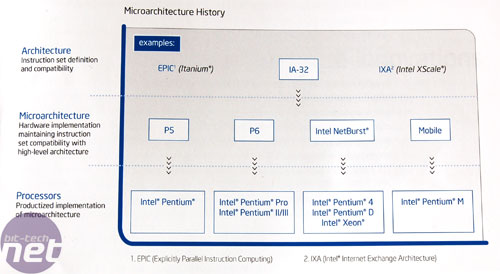

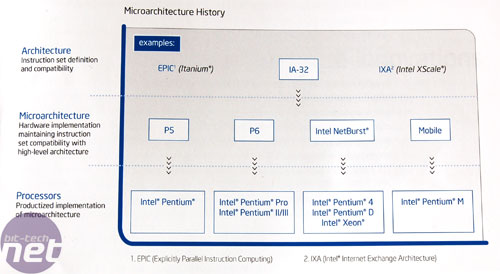

So what's a microarchitecture?

It's easiest to think of CPUs as having several different layers of instruction complexity. When a programme wants to talk to a computer, it feeds the processor standard x86 instructions - all processors on the market for PCs today are x86. There are variations on the x86 standard - for example, IA-32 is an Intel-written 32-bit version of the standard, and AMD64 is a 64-bit version of the standard. At a base level, they're all compatible. The x86 is what we call the architecture of the chip.There are also various proprietary extensions to x86, such as Intel's SSE series. These are designed to be instructions that are faster or more efficient than x86 at certain types of operations.

When the processor itself receives an x86 instruction, it splits out the instruction into micro instructions. How it splits them out will depend entirely on the microarchitecture of the chip. It splits down the instructions into simple CPU operations that are then executed, reassembled back into x86 instructions, then sent back to the programme.

Fundamentally, microarchitecture is the implementation of processor architecture in silicon.

At a simple level, if you have a very fast and efficient microarchitecture, you can process instructions faster. If you have a bad micro architecture, your CPU will be slower.

Balancing performance

The skill in designing microarchitectures is in balancing lots of factors. You can build a processor with all kinds of features, pipes and other gubbins, but it will be a power-hogging monster. You can built a microarchitecture that is really tailored to be fast at handling some instructions, but might be dog-slow at others. What is required from a microarchitecture can change over the years, as software and computer usage changes.When Intel designed the NetBurst microarchitecture for the Pentium 4, it was designed to be a performance beast. It was designed to scale very well with clock speed, and to just keep chewing through instructions. This made it a great chip for its time, but now our performance needs have changed. Its great advantage - that it scaled with clock speed - is wiped out now that we've hit 4GHz and it scales no further. It's brute force meant it ran incredibly hot.

Today's requirements for chips are now really dictated by the mobile space. Laptop computers are becoming the most popular types of computers, and obviously, brute force, hot chips are no good for this type of computer. What matters is efficient battery life and efficient use of processing power. This is why the Pentium M was created. Rather than create a chip that had a massive clock speed, and featured all kinds of features for brute force performance, Pentium M was designed to be power efficient whilst retaining high performance. It turns out that this is a fantastic way to design desktop chips too, which is why the spirit of Pentium M has very much inspired the design of the next-generation of Intel chips, based on Core.

Calculating power

We mentioned that speed is no longer just a function of clock speed. Intel defines Performance as:Performance = Frequency x Instructions per Clock Cycle.

The equation shows that performance can be improved by increasing frequency, IPC or both. The P4 worked on frequency scaling: Core works on improving the number of IPCs and frequency scaling.

However, there's a third part of this pie, which is reducing the number of instructions needed, not just processed. If you can reduce the number of things the CPU has to calculate, then you effectively increase the number of IPCs. This is where things like SSE come in, improving on the x86 instruction set.

What chips are we talking about?

The next generation of chips from Intel are codenamed Conroe, Merom and Woodcrest. They are, in order, desktop, laptop and server chips. Previously at Intel, these different markets have had different chips: the Pentium M was very different from the Pentium 4 which was very different from the Xeon. However, Intel is using the Core microarchitecture as the basis for all three of these lines going forward into the rest of the year.Despite the names, Intel's current 'new' chips - Core Duo and Core Solo - aren't based on the Core microarchitecture as such, although they have some similarities.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.