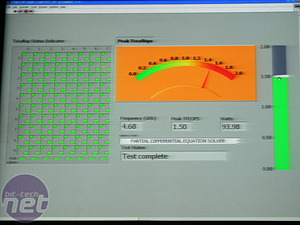

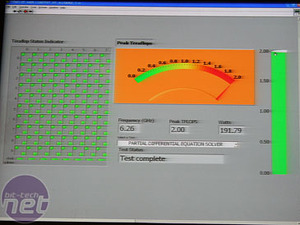

6GHz!?

Why can’t we overclock current processors to over 6GHz without sub-zero cooling then? Well, currently these cores are non IA (Intel Architecture, or x86 capable), instead they are literally just floating point (FP) processors that require special interaction through another machine with software specifically coded by the researchers at Intel.The core array also doesn’t contain any SRAM cache, which is often the limiting factor in overclocking. Thus, the Terascale project is about as far from a conventional desktop processor as you could possibly get.

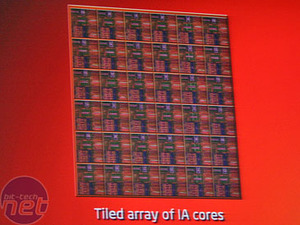

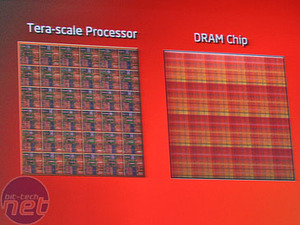

The 80-core design is a 275mm square piece of silicon, packing 100 million transistors inside. In comparison, the latest Intel quad-core processors feature 582 million transistors, while Nvidia's G80 graphics processing unit has around 691 million transistors packed inside. The array is what’s called a tiled design as the cores sit in a 10x8 array directly next to each other. We asked why Intel chose 80 cores, because usually in the computing world things scale in a factor of two.

The answer that the researchers gave us was simply because they could! They started with 64 cores on paper, but found that it was just as easy to get 80 cores working within the same transistor budget and performance target. Also, more cores mean more redundancy, meaning that if one of the cores dies, there will be much smaller cumulative performance drop.

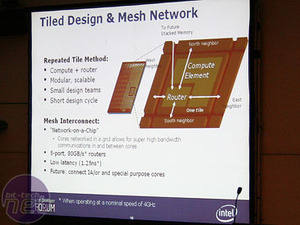

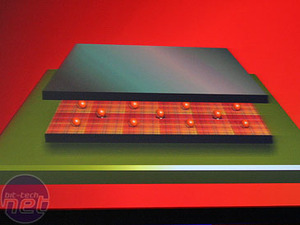

Each core contains the essential compute elements in addition to a five-way, 1.25ns low latency router capable of delivering 80GB/s of bandwidth. A single core can communicate with the other cores in all planar directions, in addition to the planned memory that will be stacked on top of the chip in the future.

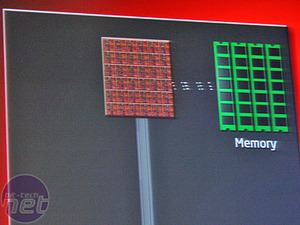

Because of the sheer number of cores in Intel's Terascale chip, it would need a massive amount of memory bandwidth to keep all of the 80 coresl fed with enough data to make the processor efficient. Thus, making a controller that's big enough and capable of passing information from cores at opposite ends of the die to said controller would be an almost impossible task.

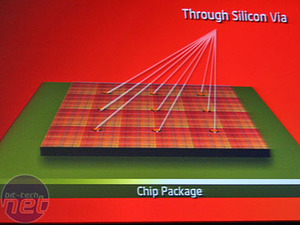

In this respect, Intel has developed a method of chip stacking, where a DRAM chip is mounted directly on top of the Terascale processor using a technique called “Through Silicon Via”. Tiny Copper channels are made through the 70-micron thick DRAM (Freya) die which is directly placed on the package substrate.

MSI MPG Velox 100R Chassis Review

October 14 2021 | 15:04

Want to comment? Please log in.